Jagd.Panther

New member

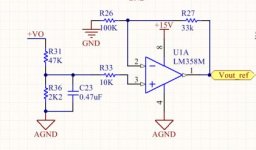

Hi cllow2020, the updated discrete driver schematic looks somewhat better. The easiest way is using high-/low-side driver with built-in interlock/dead-time generator. Other option is limit pulse width/duty cycle in MCU.View attachment 5682

how to build deadtime gardband for Q3,Q4 transient ?

else might be show as below spike will happen.

View attachment 5683

any input?

BTW there is a thread on GDT here, I posted there an example of a discrete driver with negative bias for higher dv/dt switching rates.